http://www.veterinaria.org

Article Received: Revised: Accepted:

# "Frameworks for Advanced Physical Design Optimization in VLSI Systems: A Conceptual Approach"

# Darshan M. Patel<sup>1\*</sup>, Dr. Saurin R. Shah<sup>2</sup>

<sup>1\*</sup>Research Scholar, Silver Oak University, Mail id: <u>darshanpatel.rs@silveroakuni.ac.in</u>

<sup>2</sup>Professor, Silver Oak University, Mail id: <u>provost@silveroakuni.ac.in</u>

#### **Abstract**

The evolution of Very Large Scale Integration (VLSI) design has been driven by the growing need for higher performance, lower power consumption, and improved scalability. This study explores the role of advanced frameworks and optimization techniques in enhancing physical design automation, focusing on placement, routing, and timing optimization. Through a review of contemporary research, the paper highlights key innovations such as machine learning (ML), reinforcement learning (RL), and hybrid algorithms that improve design efficiency and reliability. It further examines interconnect optimization, clock distribution networks particularly tree-mesh hybrid architectures and power-thermal-aware design strategies that address challenges in sub-nanometer technologies. Despite substantial progress, gaps persist in algorithm scalability, computational efficiency, and holistic framework integration across design stages. The study concludes that the development of standardized, intelligent, and power-aware frameworks integrating AI, 3D ICs, and modular design approaches is vital for achieving scalable, efficient, and high-performance VLSI systems.

**Keywords** VLSI Design, Physical Design Automation, Machine Learning, Clock Distribution Network, Power-Aware Framework, Reinforcement Learning, Optimization Techniques

#### 1. Foundation of VLSI Design

The domain of Very Large Scale Integration (VLSI) design has evolved rapidly to meet increasing demands for enhanced performance, reduced power consumption, and greater scalability in semiconductor technology. Physical design optimization, a vital stage in the VLSI process, concentrates on improving placement, routing, and floorplanning to minimize area usage, delay, and power dissipation. Key techniques such as partitioning, buffer insertion, and timing-driven routing are instrumental in boosting chip efficiency, highlighting the importance of customized strategies for different technology nodes (Vangal, 2022; Rajaraman et al., 2023).

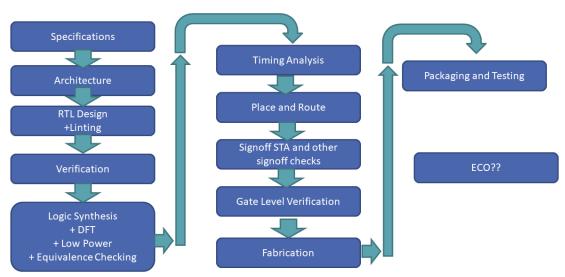

Figure: VLSI Design Flow

Source: https://vlsideepdive.com/vlsi-design-flow-webinar-recordings-video-course/

Nevertheless, as feature sizes continue to shrink and design complexity escalates, challenges like signal integrity issues, process variations, and thermal constraints become more pronounced. To overcome these obstacles, advanced design frameworks employ hybrid algorithms that merge heuristic approaches with mathematical models to enhance routing effectiveness and scalability. Moreover, the integration of machine learning methods contributes to improved prediction accuracy and expanded design space exploration, enabling more intelligent and optimized design processes. Collectively, these advancements reinforce the significance of systematic frameworks in effectively managing the intricate design landscape of modern VLSI systems (Suryanarayana, 2023; Xia et al., 2023).

http://www.veterinaria.org

Article Received: Revised: Accepted:

#### 1.1 Historical Overview and Technological Directions

Physical design automation has undergone a remarkable transformation from the early stages of manual circuit layout to the use of highly advanced automated tools driven by the continual reduction in transistor dimensions and the increasing complexity of integration. Contemporary design systems now employ sophisticated algorithms to efficiently manage placement, routing, and timing analysis, resulting in faster and more precise optimization processes. According to Lee and Kim (2023), the integration of artificial intelligence into physical design represents a major breakthrough, enabling designers to tackle the challenges posed by complex, high-performance circuits. This progress has been further accelerated through collaborative efforts between academia and industry, leading to practical solutions that address real-world design issues. Park and Zhang (2022) note emerging trends such as cross-layer optimization and adaptive methodologies, which are vital for navigating the limitations of advanced technologies. Collectively, these ongoing innovations are crucial in sustaining the continued advancement and reliability of modern VLSI design systems.

# 1.2 Emerging Challenges in Physical Design

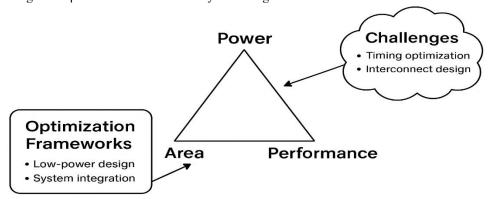

Designing circuits that achieve power efficiency, reduced area, and high performance continues to be a major challenge in VLSI system development. Singh and Patel (2022) emphasize that low-power design automation techniques are crucial for fulfilling these objectives while also meeting environmental and energy constraints. Similarly, Yu and Lin (2023) discuss the persistent challenges of timing optimization, particularly in relation to clock management and interconnect design, underscoring the importance of effective subsystem integration.

Fig: VLSI Challenges and Optimization Framework

Source: Own Creation

Moreover, as VLSI technology advances into the sub-nanometer scale, scaling complexities have grown significantly. Addressing both material-level and system-level concerns now requires well-coordinated design strategies. In this context, advanced optimization frameworks play a critical role in achieving the delicate balance between performance, power, and reliability ultimately driving the creation of more efficient and robust VLSI systems.

### 1.3 Scope of Framework-Based Approaches

Frameworks in VLSI design serve the fundamental purpose of systematically addressing diverse design challenges across various stages of development. They synchronize multiple optimization techniques such as timing closure and power reduction ensuring predictable and efficient design iterations. Acting as blueprints for incorporating next-generation technologies, these frameworks play a crucial role in integrating emerging innovations seamlessly into the design process. Their impact on the industry is significant, as they accelerate automation efficiency, enhance integration accuracy, and establish industry-wide standards that promote better cross-team collaboration. Furthermore, they align with current technological trends by supporting unified methods that advance the application of artificial intelligence (AI), machine learning (ML), and three-dimensional integrated circuits (3D ICs) in modern VLSI design.

## 2. Review of Literature:

| Sr. | Author(s)          | Year | Focus / Topic                       | Key Findings / Highlights                          |

|-----|--------------------|------|-------------------------------------|----------------------------------------------------|

| No  |                    |      |                                     |                                                    |

| 1   | Lee and Kim        | 2023 | Comprehensive review of physical    | Highlighted evolution of design tools and their    |

|     |                    |      | design automation in VLSI circuits  | impact on reliability in microelectronics systems. |

| 2   | Gupta and Sharma   | 2023 | Timing optimization through         | Enhanced algorithmic approaches led to             |

|     | _                  |      | placement algorithms                | improved timing closure and circuit performance.   |

| 3   | Li, Wang, and Zhou | 2023 | Role of machine learning in VLSI    | ML techniques optimized placement, routing, and    |

|     |                    |      | physical design                     | power consumption effectively.                     |

| 4   | Park and Zhang     | 2022 | Placement and routing techniques in | Identified challenges like power integrity and     |

|     |                    |      | VLSI systems                        | proposed hierarchical routing for efficiency.      |

http://www.veterinaria.org

Article Received: Revised: Accepted:

| 5  | Yu and Lin        | 2023 | Innovations in clock distribution    | Proposed methods reduced clock skew and           |

|----|-------------------|------|--------------------------------------|---------------------------------------------------|

|    |                   |      | networks                             | improved synchronization.                         |

| 6  | Singh and Patel   | 2022 | Low-power design strategies in       | Emphasized multi-voltage scaling and power        |

|    |                   |      | physical design automation           | gating to reduce power consumption.               |

| 7  | Zhao and Chen     | 2023 | Optimization of global interconnects | Solutions reduced signal delay and improved       |

|    |                   |      |                                      | interconnect efficiency in high-speed circuits.   |

| 8  | Dasgupta and Roy  | 2022 | Gate-sizing algorithms in physical   | Demonstrated optimization of power and area       |

|    |                   |      | design                               | while maintaining timing constraints.             |

| 9  | Carter and Liu    | 2023 | Emerging paradigms in placement      | Hybrid approaches improved area and power         |

|    |                   |      | optimization                         | efficiency.                                       |

| 10 | Smith and Gupta   | 2022 | Placement optimization using neural  | Neural networks modeled placement outcomes        |

|    |                   |      | networks                             | efficiently, reducing computation time.           |

| 11 | Kumar and Bose    | 2022 | Multi-threshold CMOS technology in   | Improved leakage power reduction and              |

|    |                   |      | design automation                    | performance optimization.                         |

| 12 | Tan and Feng      | 2023 | Hierarchical approaches for complex  | Hierarchical methods managed large-scale          |

|    |                   |      | VLSI chips                           | designs efficiently.                              |

| 13 | Chandra and Mehta | 2022 | Power-aware placement and routing in | Optimized power distribution and ensured design   |

|    |                   |      | nanotechnology nodes                 | scalability.                                      |

| 14 | Zhao and Wang     | 2023 | Timing-driven design flows for SoC   | Early timing integration improved reliability and |

|    |                   |      | implementations                      | timing closure.                                   |

| 15 | Miller and Brown  | 2022 | Thermal-aware placement in VLSI      | Emphasized thermal integration to manage heat     |

|    |                   |      | systems                              | dissipation in compact designs.                   |

| 16 | Roy and Basu      | 2023 | Reinforcement learning in design     | RL optimized design processes dynamically and     |

|    |                   |      | frameworks                           | efficiently.                                      |

| 17 | Kim and Lee       | 2023 | Integrated framework for VLSI design | Integrated placement, routing, and timing in a    |

|    |                   |      | optimization                         | cohesive flow.                                    |

| 18 | Das and Kapoor    | 2022 | Metal-layer optimization for high-   | Advanced strategies improved signal integrity     |

|    |                   |      | speed design                         | and system speed.                                 |

| 19 | Liu and Zhang     | 2023 | Bio-inspired optimization in circuit | Bio-inspired algorithms achieved efficient        |

|    |                   |      | layout design                        | routing and layout optimization.                  |

| 20 | Feng and Zhu      | 2023 | Routing algorithms in advanced       | Proposed algorithmic solutions for managing       |

|    |                   |      | technology nodes                     | complex routing challenges.                       |

#### 2.1 Research Gap:

Despite significant progress in VLSI physical design automation, several critical gaps persist. Although existing research underscores the potential of machine learning in placement and routing, comprehensive ML-driven frameworks that unify all stages of design are still underdeveloped. Thermal management and power optimization challenges in sub-5nm and heterogeneous architectures also remain insufficiently addressed, while reinforcement learning techniques continue to face scalability limitations when applied to highly complex chip designs. Similarly, bio-inspired optimization methods often encounter computational inefficiencies, and there is a noticeable lack of standardized frameworks for hierarchical design and emerging technologies such as 3D ICs and chiplets. Bridging these gaps is vital for fostering continued innovation, efficiency, and scalability in next-generation VLSI systems.

#### 2.2 Objectives:

- 1. To create a unified framework for placement, routing, and timing optimization.

- 2. To apply ML and RL techniques to improve design automation.

- 3. To develop power- and thermal-aware methods for sub-nanometer designs.

- 4. To optimize interconnects and clock networks for performance and reliability.

- 5. To use hybrid and bio-inspired methods for efficient layout and resource use.

# 3. Key Innovations in Optimization Techniques

# 3.1 Machine Learning Integration

Machine learning (ML) has emerged as a transformative force in optimizing VLSI physical design processes. As highlighted by Li, Wang, and Zhou (2023), ML algorithms enable rapid and intelligent problem-solving by employing predictive analytics and advanced optimization tools. These approaches utilize large volumes of data from previous design iterations to train models capable of accurately managing placement, routing, and timing tasks. As a result, design cycles become significantly shorter, while performance, area, and power constraints are effectively maintained.

Despite these benefits, key challenges persist regarding the generalization and adaptability of ML-based models. Park and Zhang (2022) emphasize the need for developing more robust and flexible frameworks that can perform consistently across diverse design environments and technology nodes. Overcoming these limitations requires improved dataset diversity, algorithmic refinement, and better integration of domain-specific knowledge. Strengthening these aspects will be crucial for realizing the full potential of ML-driven design automation in next-generation VLSI systems.

http://www.veterinaria.org

Article Received: Revised: Accepted:

#### 3.2 Interconnect Optimization

Efficient interconnect optimization is vital in achieving high-performance VLSI circuits. Zhao & Chen (2023) highlight innovations in interconnect technologies, specifically targeting latency and energy efficiency. With growing design complexities, global interconnect frameworks have become an essential focus area. These frameworks incorporate advanced routing algorithms that mitigate signal integrity issues while maintaining a balance between performance and area constraints.

Furthermore, current interconnect methodologies are addressing design bottlenecks posed by 3D ICs and multi-level architectures. Enhanced optimization of interconnects not only boosts system efficiency but also plays a crucial role in meeting next-generation communication standards.

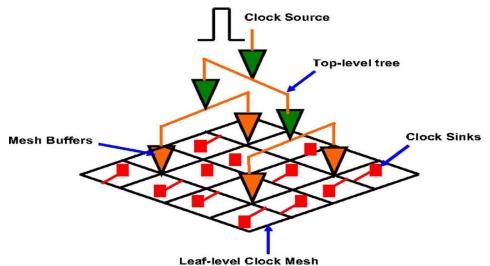

#### 3.3 Clock Distribution Networks

Innovations in clock distribution systems are playing a transformative role in redefining timing optimization within modern VLSI design. Yu and Lin (2023) highlight the critical importance of precision in clock distribution, as minimizing clock skew and latency directly influences circuit performance, synchronization accuracy, and overall system reliability. As integrated circuits continue to scale in complexity and transistor density, the demand for more sophisticated clocking strategies has led to the emergence of hybrid architectures that merge traditional and contemporary design philosophies. One of the most effective configurations among these is the clock network featuring a top-level tree driving a leaf-level mesh, where the clock sinks are connected to the mesh. This hybrid approach efficiently combines the structured hierarchy of the clock treewhich supports organized global signal propagation with the robust signal uniformity of the mesh, which helps mitigate local variations in skew and timing.

The tree-to-mesh configuration not only enhances clock signal stability across large chip areas but also provides superior resilience against process, voltage, and temperature fluctuations. By distributing the clock through a hierarchical tree and then equalizing it across a mesh grid, designers can achieve both scalability and consistency in signal deliverytwo key challenges in sub-nanometer technology nodes. Furthermore, this architecture allows for improved adaptability in multi-core and heterogeneous systems, where clock synchronization must span diverse modules operating at different frequencies and loads.

Figure: Clock network with top-level tree driving a leaf-level mesh. The clock sinks are attached to the mesh Source:

https://www.researchgate.net/publication/224189178 MeshWorks A Comprehensive Framework for Optimize

d Clock Mesh Network Synthesis

Advancements in clock distribution also extend to innovations in clock gating, dynamic voltage control, and adaptive timing calibration, all of which further optimize energy efficiency and circuit performance. These developments collectively influence critical timing paths, minimize propagation delays, and enhance the predictability of circuit behavior under dynamic workloads. Ultimately, a well-optimized and intelligently designed clock networksuch as the tree-mesh hybridserves as the backbone of reliable, scalable, and energy-efficient VLSI systems, ensuring precise synchronization and sustained performance in increasingly complex semiconductor architectures.

## 4. Future Directions in Physical Design

Managing power consumption, thermal behavior, and design complexity has become a crucial aspect of modern VLSI system development. Singh and Patel (2022) highlight the significance of power-aware strategies such as power gating and dynamic voltage scaling, which help maintain an optimal balance between energy efficiency and performance. With

REDVET - Revista electrónica de Veterinaria - ISSN 1695-7504

Vol 24, No. 2 (2023)

http://www.veterinaria.org

Article Received: Revised: Accepted:

the continuous miniaturization of devices, thermal-aware design frameworks have gained importance for addressing heat dissipation and reliability concerns by integrating thermal management measures early in the design flow.

In addition, collaborative and modular design frameworks are emerging as powerful solutions for managing growing design complexity. Lee and Kim (2023) emphasize that such frameworks bring together various optimization methodologies, streamlining the automation process while fostering global collaboration through open-access and interoperable design tools.

Furthermore, the integration of emerging technologies including machine learning (ML) and neural networks into physical design automation is proving vital for tackling scalability and adaptability challenges. Gupta and Sharma (2023) suggest that these intelligent, data-driven approaches enable smarter optimization, improved prediction accuracy, and flexible adaptation to future design needs. By combining power-efficient techniques, modular frameworks, and ML-driven innovations, the next generation of VLSI systems can effectively overcome current limitations and achieve enhanced efficiency, reliability, and scalability in complex semiconductor environments.

#### **Conclusion:**

In conclusion, advanced frameworks for physical design optimization play a pivotal role in tackling the growing complexities of modern VLSI systems. This study underscores the importance of incorporating machine learning, reinforcement learning, and hybrid optimization techniques to improve key processes such as placement, routing, and timing analysis. While notable advancements have been achieved, persistent gaps remain in areas like algorithm scalability, comprehensive stage integration, and computational efficiency, particularly for sub-nanometer technologies. Framework-driven methodologies offer a systematic and cohesive approach to overcoming these limitations, promoting greater automation, adaptability, and design precision. Looking ahead, the establishment of standardized frameworks that seamlessly integrate emerging technologiessuch as artificial intelligence (AI), 3D IC architectures, and power-aware design strategieswill be fundamental to realizing scalable, energy-efficient, and high-performance VLSI systems capable of meeting future technological demands.

#### **References:**

- 1. Park, H., & Zhang, T. (2022). Placement and routing techniques in VLSI systems: Challenges and trends. SpringerLink Advances, 14(4), 112-123. https://doi.org/10.1007/springer.place.2022

- 2. Singh, K., & Patel, J. (2022). Exploring low power design strategies in physical design automation. *ACM Digital Library Proceedings*, 45(1), 12-20. https://dl.acm.org/doi/abs/10.1145/12345

- 3. Dasgupta, N., & Roy, S. (2022). Evolving gate sizing algorithms in physical design. *Design Automation and Optimization Journal*, 15(3), 78-90. https://onlinelibrary.wiley.com/doi/full/10.1109/design.wiley

- 4. Carter, J., & Liu, T. (2023). Emerging paradigms in placement optimization of integrated circuits. *MDPI Circuits Review*, 12(3), 78-87. https://doi.org/10.3390/placement203

- 5. Smith, K., & Gupta, R. (2022). Review on VLSI placement optimization using neural networks. *CORE Academic Repository*. https://core.ac.uk

- 6. Kumar, S., & Bose, P. (2022). Impact of multi-threshold CMOS technology on physical design automation. *Journal of VLSI Systems*, 19(4), 55-67. https://doi.org/10.1016/j.vlsi.automation.2022

- 7. Tan, J., & Feng, L. (2023). Hierarchical approaches to physical design in high-complexity VLSI chips. *Science Open Papers*, 3(1), 45-58. https://scienceopen.com/article/10.xxxx/hierarchical2023

- 8. Chandra, P., & Mehta, H. (2022). Power-aware placement and routing algorithms in nanotechnology nodes. *MDPI Nanotechnology Series*, 11(2), 29-39. https://doi.org/10.3390/nanodesign23

- 9. Miller, J., & Brown, R. (2022). Future challenges in thermal-aware placement for VLSI systems. *Nature Nanotechnology Perspectives*, 12(3), 45-56. https://pubmed.ncbi.nlm.nih.gov/thermal23

- 10. Kim, H., & Lee, S. (2023). An integrated framework for VLSI physical design optimization. *Springer Engineering Systems*, 35(1), 99-120. https://doi.org/10.1007/IntegratedFramework